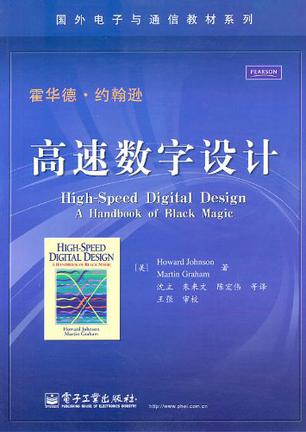

高速数字设计txt,chm,pdf,epub,mobi下载 高速数字设计txt,chm,pdf,epub,mobi下载作者:(美)约翰逊//格雷厄姆|译者 出版社: 电子工业 出版年: 2010-4 页数: 355 定价: 39.80元 ISBN: 9787121104701 内容简介 · · · · · ·《高速数字设计》是信号完整性领域的一部经典著作,其英文版已重印超过20次。《高速数字设计》结合了数字和模拟电路理论,对高速数字电路系统设计中的信号完整性和EMC方面的问题进行了深入浅出的讨论和研究.其中不仅包括关于高速数字设计中EMC方面的许多实用信息,还包括许多有价值的测试技术。另外,书中详细讨论了涉及信号完整性方面的传输线、时钟偏移和抖动、端接、过孔等问题。《高速数字设计》综合了数字和模拟设计技术,对数字电路设计人员提高设计技能、缩短其产品的开发周期、精通信号完整性技术等都大有裨益。 《高速数字设计》将理论与实践方法相结合,适合从事模拟和数字电路设计的相关人员使用,可作为大专院校相关专业师生的教学参考,同时也适合体系结构设计人员、EMC专家、印刷电路板设计和布线专业人士阅读。 作者简介 · · · · · ·Howard Johnson 1982年在美国莱斯大学获得博士学位后专攻高速数字通信和数字信号处理系统的设计,在数字设计领域有近30年的经验。一直从事数字电子设计和咨询业务,服务于全球的数字工程师,并在英国牛津大学授课。 目录 · · · · · ·第1章 基础知识 1.1 频率与时间 1.2 时间与距离 1.3 集总与分布系统 1.4 关于3 dB和RMS频率的解释 1.5 4种类型的电抗 1.6 普通电容 1.7 普通电感 1.8 估算衰减时间的更好方法 1.9 互容 1.10 互感第2章 逻辑门电路的高速特性 2.1 一种年代久远的数字技术的发展历史 2.2 功耗 2.3 速度 2.4 封装第3章 测量技术 3.1 示波器探头的上升时问和带宽 3.2 探头接地环路的自感 3.3 探头接地环路检测到的假信号 3.4 探头是如何加重电路负载的 3.5 特殊的探头构造 3.6 避免检测到来自探头外壳电流的信号 3.7 观测一个串行数据传输系统 3.8 降低系统时钟 3.9 观测串扰 3.10 测量工作容限 3.11 观察亚稳态第4章 传输线 4.1 普通点对点布线的缺点 4.2 无限均匀传输线 4.3 源端及负载阻抗的影响 4.4 传输线的特殊实例 4.5 线路阻抗和传播延迟第5章 地平面和叠层 5.1 高速电流沿着电感最小路径前进 5.2 完整地平面的串扰 5.3 开槽地平面的串扰 5.4 平行交叉地平面的串扰 5.5 指状电源和地线的串扰 5.6 保护走线 5.7 近端和远端串扰 5.8 印刷电路板如何叠层第6章 端接 6.1 末端端接器 6.2 源端端接器 6.3 中间端接器 6.4 末端端接器的交流偏置 6.5 电阻的选择 6.6 端接器中的串扰第7章 通孔 7.1 通孔的机械特性 7.2 通孔的电容 7.3 通孔的电感 7.4 返回电流及其与通孔的关系第8章 电源系统 8.1 提供稳定的电压参考 8.2 分配统一的电压 8.3 一般情形的电源分配问题 8.4 选择旁路电容第9章 连接器 9.1 互感——连接器如何引起串扰 9.2 串联电感——连接器怎样产生电磁干扰 9.3 寄生电容——用在多支路总线上的连接器 9.4 连接器中耦合的测量 9.5 连接器下地平面的连续性 9.6 采用外部连接解决EMI问题 9.7 高速应用的特殊连接器 9.8 穿过连接器的差分信号 9.9 连接器的电源管理特性第10章 扁平电缆 10.1 扁平电缆的信号传播 10.2 扁平电缆的串扰 10.3 扁平电缆连接器 10.4 扁平电缆的电磁干扰第11章 时钟分配 11.1 定时裕量 11.2 时钟偏移 11.3 使用低阻抗驱动器 11.4 使用低阻抗的时钟分配线 11.5 多路时钟线的源端端接 11.6 控制时钟线上的串扰 11.7 延时的调整 11.8 差分信号分配 11.9 时钟信号的占空比 11.10 消除时钟中继器的寄生电容 11.11 时钟总线上时钟接收器的去耦第12章 时钟振荡器 12.1 使用罐装的时钟振荡器 12.2 时钟抖动附录A 记忆要点附录B 计算上升时间附录C MathCAD公式参考书目索引第1章 基础知识 1.1 频率与时间 1.2 时间与距离 1.3 集总与分布系统 1.4 关于3 dB和RMS频率的解释 1.5 4种类型的电抗 1.6 普通电容 1.7 普通电感 1.8 估算衰减时间的更好方法 1.9 互容 1.10 互感第2章 逻辑门电路的高速特性 2.1 一种年代久远的数字技术的发展历史 2.2 功耗 2.3 速度 2.4 封装第3章 测量技术 3.1 示波器探头的上升时问和带宽 3.2 探头接地环路的自感 3.3 探头接地环路检测到的假信号 3.4 探头是如何加重电路负载的 3.5 特殊的探头构造 3.6 避免检测到来自探头外壳电流的信号 3.7 观测一个串行数据传输系统 3.8 降低系统时钟 3.9 观测串扰 3.10 测量工作容限 3.11 观察亚稳态第4章 传输线 4.1 普通点对点布线的缺点 4.2 无限均匀传输线 4.3 源端及负载阻抗的影响 4.4 传输线的特殊实例 4.5 线路阻抗和传播延迟第5章 地平面和叠层 5.1 高速电流沿着电感最小路径前进 5.2 完整地平面的串扰 5.3 开槽地平面的串扰 5.4 平行交叉地平面的串扰 5.5 指状电源和地线的串扰 5.6 保护走线 5.7 近端和远端串扰 5.8 印刷电路板如何叠层第6章 端接 6.1 末端端接器 6.2 源端端接器 6.3 中间端接器 6.4 末端端接器的交流偏置 6.5 电阻的选择 6.6 端接器中的串扰第7章 通孔 7.1 通孔的机械特性 7.2 通孔的电容 7.3 通孔的电感 7.4 返回电流及其与通孔的关系第8章 电源系统 8.1 提供稳定的电压参考 8.2 分配统一的电压 8.3 一般情形的电源分配问题 8.4 选择旁路电容第9章 连接器 9.1 互感——连接器如何引起串扰 9.2 串联电感——连接器怎样产生电磁干扰 9.3 寄生电容——用在多支路总线上的连接器 9.4 连接器中耦合的测量 9.5 连接器下地平面的连续性 9.6 采用外部连接解决EMI问题 9.7 高速应用的特殊连接器 9.8 穿过连接器的差分信号 9.9 连接器的电源管理特性第10章 扁平电缆 10.1 扁平电缆的信号传播 10.2 扁平电缆的串扰 10.3 扁平电缆连接器 10.4 扁平电缆的电磁干扰第11章 时钟分配 11.1 定时裕量 11.2 时钟偏移 11.3 使用低阻抗驱动器 11.4 使用低阻抗的时钟分配线 11.5 多路时钟线的源端端接 11.6 控制时钟线上的串扰 11.7 延时的调整 11.8 差分信号分配 11.9 时钟信号的占空比 11.10 消除时钟中继器的寄生电容 11.11 时钟总线上时钟接收器的去耦第12章 时钟振荡器 12.1 使用罐装的时钟振荡器 12.2 时钟抖动附录A 记忆要点附录B 计算上升时间附录C MathCAD公式参考书目索引 · · · · · · () |

首页

首页

怎么说呢,感觉这本书涉及的方方面面太多

忍不住一直看下去

作者视角观点都是很独特,现在只看了一部分,相信不会辜负自己的

有思想